# Lecture Notes in Computer Science

2606

Edited by G. Goos, J. Hartmanis, and J. van Leeuwen

# Springer Berlin

Berlin Heidelberg New York Barcelona Hong Kong London Milan Paris Tokyo Andy M. Tyrrell Pauline C. Haddow Jim Torresen (Eds.)

# Evolvable Systems: From Biology to Hardware

5th International Conference, ICES 2003 Trondheim, Norway, March 17-20, 2003 Proceedings

#### Series Editors

Gerhard Goos, Karlsruhe University, Germany Juris Hartmanis, Cornell University, NY, USA Jan van Leeuwen, Utrecht University, The Netherlands

#### Volume Editors

Andy M. Tyrrell

The University of York, The Department of Electronics Heslington, York YO10 5DD, United Kingdom

E-mail: amt@ohm.york.ac.uk

Pauline C. Haddow

The Norwegian University of Science and Technology Department of Computer and Information Science Sem Sælands Vei, 7491 Trondheim, Norway

E-mail: pauline@idi.ntnu.no

Jim Torresen University of Oslo, Department of Informatics P.O. Box 1080 Blindern, 0316 Oslo, Norway

E-mail: jimtoer@ifi.uio.no

Cataloging-in-Publication Data applied for

A catalog record for this book is available from the Library of Congress

Bibliographic information published by Die Deutsche Bibliothek Die Deutsche Bibliothek lists this publication in the Deutsche Nationalbibliographie; detailed bibliographic data is available in the Internet at <a href="http://dnb.ddb.de">http://dnb.ddb.de</a>>.

CR Subject Classification (1998): B.6, B.7, F.1, I.6, I.2, J.2, J.3

ISSN 0302-9743

ISBN 3-540-00730-X Springer-Verlag Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer-Verlag. Violations are liable for prosecution under the German Copyright Law.

Springer-Verlag Berlin Heidelberg New York a member of BertelsmannSpringer Science+Business Media GmbH

http://www.springer.de

© Springer-Verlag Berlin Heidelberg 2003 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Olgun Computergraphik Printed on acid-free paper SPIN: 10872784 06/3142 5 4 3 2 1 0

# **Preface**

The idea of evolving machines, whose origins can be traced to the cybernetics movement of the 1940s and 1950s, has recently resurged in the form of the nascent field of bio-inspired systems and evolvable hardware. The inaugural workshop, Towards Evolvable Hardware, took place in Lausanne in October 1995, followed by the First International Conference on Evolvable Systems: From Biology to Hardware (ICES), held in Tsukuba, Japan in October 1996. The second ICES conference was held in Lausanne in September 1998, with the third and fourth being held in Edinburgh, April 2000 and Tokyo, October 2001 respectively. This has become the leading conference in the field of evolvable systems and the 2003 conference promised to be at least as good as, if not better than, the four that preceded it.

The fifth international conference was built on the success of its predecessors, aiming at presenting the latest developments in the field. In addition, it brought together researchers who use biologically inspired concepts to implement real systems in artificial intelligence, artificial life, robotics, VLSI design and related domains. We would say that this fifth conference followed on from the previous four in that it consisted of a number of high-quality interesting thought-provoking papers.

We received 58 papers in total. All of these papers were reviewed by three independent reviewers. As such, we feel that we compiled an excellent package for ICES 2003. The conference included 3 keynote talks titled: "Nano- and biotechnology," "From wheels to wings with evolutionary spiking neurons," and "Machine design of quantum computers: A new frontier." We had 41 technical presentations, a panel debate, and 3 tutorials in the areas of: evolutionary algorithms, evolvable hardware and reconfigurable devices, and nanotechnology. In addition to the technical program, there was a strong and varied social program both during and after the conference.

We would like to thank the reviewers for their time and effort in reviewing all of the submitted papers. We would also like to thank the other members of the organizing committee, including the local chair Keith Downing and publicity chair Gunnar Tufte. We are most grateful to Frode Eskelund, Diego Federici, and Karstein A. Kristiansen for their great help in developing the web-based paper submission and registration tool. We wish to thank the following for their contribution to the success of this conference: The Research Council of Norway; European Community IST programme; Norwegian University of Science and Technology; University of Oslo; European Office of Aerospace Research and Development, Air Force Office of Scientific Research, United States Air Force Research Laboratory; Telenor ASA; Atmel; and Siemens. Finally, we would like to thank all of those authors who put so much effort into their research and decided to publish their work at our conference.

#### VI Preface

What topics might we consider important for the next few years? It is clear that the field is still developing, evolving, and that many of the "hot" topics at this conference will be seen again next time. These will include: evolutionary hardware design; co-evolution of hybrid systems; evolving hardware systems; intrinsic, and on-line evolution; hardware/software co-evolution; self-repairing hardware; self-reconfiguring hardware; embryonic hardware; morphogenesis; novel devices; adaptive computing; and of course we are always looking for, and interested in, real-world applications of evolvable hardware. Will we see breakthroughs relating to nanotechnology, new reconfigurable FPGAs and new models of reliability for long space missions? Only time will tell – as with all evolution.

We hope you enjoy reading these proceedings as much as we enjoyed putting them together.

January 2003

Andy M. Tyrrell Pauline C. Haddow Jim Torresen

# Organization

# Organizing Committee

General Chair: Andy M. Tyrrell (University of York, UK)

Program Co-chair: Pauline C. Haddow (Norwegian University of

Science and Technology, Norway)

Program Co-chair: Jim Torresen (University of Oslo, Norway) Local Chair: Keith Downing (Norwegian University of

Science and Technology, Norway)

Publicity Chair: Gunnar Tufte (Norwegian University of Science

and Technology, Norway)

# **International Steering Committee**

Tetsuya Higuchi, National Institute of Advanced Industrial Science and Technology (AIST), Japan

Daniel Mange, Swiss Federal Institute of Technology, Switzerland

Julian Miller, University of Birmingham, UK

Moshe Sipper, Ben-Gurion University, Israel

Adrian Thompson, University of Sussex, UK

# **Program Committee**

Juan Manuel Moreno Arostegui, Universitat Politecnica de Catalunya, Spain

Wolfgang Banzhaf, University of Dortmund, Germany

Peter J. Bentley, University College London, UK

Gordon Brebner, Xilinx, USA

Richard Canham, University of York, UK

Stefano Cagnoni, Universita' di Parma, Italy

Prabhas Chongstitvatana, Chulalongkorn University, Thailand

Carlos A. Coello Coello, LANIA, Mexico

Peter Dittrich, University of Dortmund, Germany

Marco Dorigo, Université Libre de Bruxelles, Belgium

Keith Downing, Norwegian University of Science and Technology, Norway

Rolf Drechsler, University of Bremen, Germany

Marc Ebner, Universität Würzburg, Germany

Stuart J. Flockton, University of London, UK

Dario Floreano, Swiss Federal Institute of Technology, Switzerland

Terence C. Fogarty, South Bank University, UK

David B. Fogel, Natural Selection, Inc., USA

Andrew Greenstead, University of York, UK

#### VIII Organization

Hugo deGaris, Utah State University, USA

Tim Gordon, University College London, UK

Darko Grundler, Univesity of Zagreb, Croatia

Pauline C. Haddow, Norwegian University of Science and Technology, Norway

David M. Halliday, University of York, UK

Alister Hamilton, University of Edinburgh, UK

Arturo Hernandez Aguirre, Tulane University, USA

Francisco Herrera, University of Granada, Spain

Jean-Claude Heudin, Pule Universitaire Léonard de Vinci, France

Tetsuya Higuchi, National Institute of Advanced Industrial Science and Technology (AIST), Japan

Hitoshi Iba, University of Tokyo, Japan

Masaya Iwata, National Institute of Advanced Industrial Science and Technology (AIST), Japan

Alex Jackson, University of York, UK

Tatiana Kalganova, Brunel University, UK

Didier Keymeulen, Jet Propulsion Laboratory, USA

Michael Korkin, Genobyte, Inc., USA

Sanjeev Kumar, University College London, UK

William B. Langdon, University College London, UK

Yong Liu, University of Aizu, Japan

Jason Lohn, NASA Ames Research Center, USA

Michael Lones, University of York, UK

Evelyne Lutton, INRIA, France

Daniel Mange, Swiss Federal Institute of Technology, Switzerland

Karlheinz Meier, Heidelberg University, Germany

Julian Miller, University of Birmingham, UK

David Montana, BBN Technologies, USA

Masahiro Murakawa, National Institute of Advanced Industrial Science and Technology (AIST), Japan

Marek A. Perkowski, Portland State University, USA

Matteo Sonza Reorda, Politecnico di Torino, Italy

Mehrdad Salami, School of Biophysical Sciences and Electrical Engineering, Australia

Eduardo Sanchez, Swiss Federal Institute of Technology, Switzerland

Lukas Sekanina, Brno University of Technology, Czech Republic

Moshe Sipper, Ben-Gurion University, Israel

Giovanni Squillero, Politecnico di Torino, Italy

Andre Stauffer, Swiss Federal Institute of Technology, Switzerland

Adrian Stoica, Jet Propulsion Laboratory, USA

Kiyoshi Tanaka, Shinshu University, Japan

Gianluca Tempesti, Swiss Federal Institute of Technology, Switzerland

Christof Teuscher, Swiss Federal Institute of Technology, Switzerland

Jonathan Timmis, University of Kent, UK

Adrian Thompson, University of Sussex, UK

Peter Thomson, Napier University, UK

Jim Torresen, University of Oslo, Norway Gunnar Tufte, Norwegian University of Science and Technology, Norway Andy Tyrrell, University of York, UK Piet van Remortel, Vrije Universiteit Brussel (VUB), Brussels, Belgium Milan Vasilko, Bournemouth University, UK Xin Yao, University of Birmingham, UK Moritoshi Yasunaga, University of Tsukuba, Japan Ricardo S. Zebulum, Jet Propulsion Laboratory, USA

# **Sponsoring Institutions**

We wish to thank the following for their contribution to the success of this conference:

The Research Council of Norway

European Community IST programme (Fifth Framework Programme)

Department of Computer and Information Science, Norwegian University of Science and Technology

Department of Informatics, University of Oslo

European Office of Aerospace Research and Development, Air Force Office of Scientific Research, United States Air Force Research Laboratory

Telenor ASA

Atmel

Siemens

# **Table of Contents**

| Evolution                                                                                             |

|-------------------------------------------------------------------------------------------------------|

| On Fireflies, Cellular Systems, and Evolware                                                          |

| A Comparison of Different Circuit Representations for Evolutionary Analog Circuit Design              |

| Fault Tolerance and Fault Recovery                                                                    |

| Fault Tolerance via Endocrinologic Based Communication for Multiprocessor Systems                     |

| Using Negative Correlation to Evolve Fault-Tolerant Circuits                                          |

| A Genetic Representation for Evolutionary Fault Recovery in Virtex FPGAs                              |

| Development                                                                                           |

| Biologically Inspired Evolutionary Development                                                        |

| Building Knowledge into Developmental Rules for Circuit Design 69  Gunnar Tufte and Pauline C. Haddow |

| Evolving Fractal Proteins                                                                             |

| A Developmental Method for Growing Graphs and Circuits                                                |

| Developmental Models for Emergent Computation                                                         |

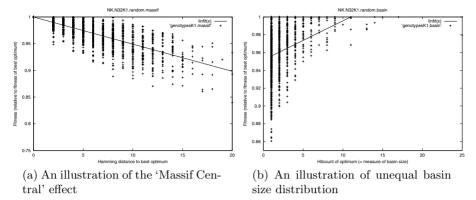

| Developmental Effects on Tuneable Fitness Landscapes                                                  |

Tom Lenaerts, and Bernard Manderick

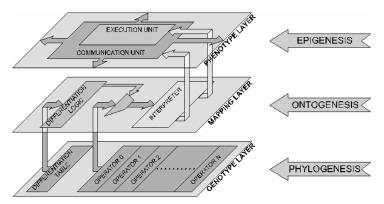

# **POEtic**

| POEtic Tissue: An Integrated Architecture for Bio-inspired Hardware 129<br>Andy M. Tyrrell, Eduardo Sanchez, Dario Floreano,<br>Gianluca Tempesti, Daniel Mange, Juan-Manuel Moreno,<br>Jay Rosenberg, and Alessandro E.P. Villa |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

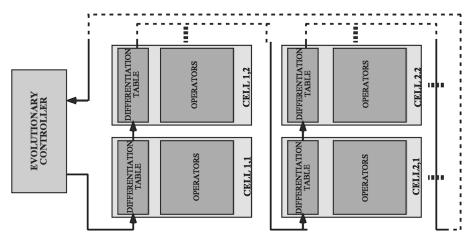

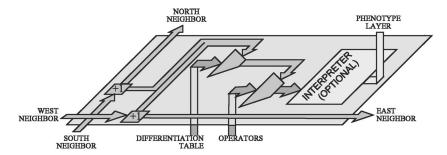

| Ontogenetic Development and Fault Tolerance in the POEtic Tissue 141 Gianluca Tempesti, Daniel Roggen, Eduardo Sanchez, Yann Thoma, Richard Canham, and Andy M. Tyrrell                                                          |

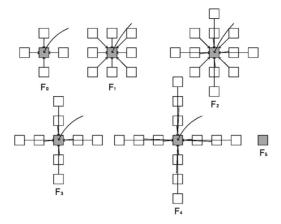

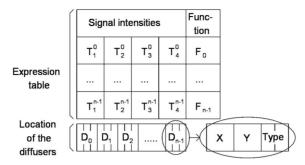

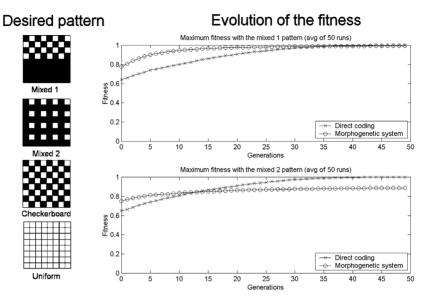

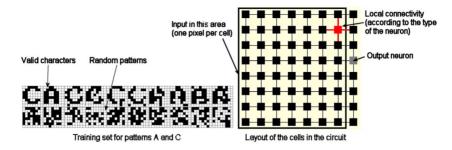

| A Morphogenetic Evolutionary System: Phylogenesis of the POEtic Circuit                                                                                                                                                          |

| Spiking Neural Networks for Reconfigurable POEtic Tissue                                                                                                                                                                         |

| A Learning, Multi-layered, Hardware Artificial Immune System Implemented upon an Embryonic Array                                                                                                                                 |

| Applications 1                                                                                                                                                                                                                   |

| Virtual Reconfigurable Circuits for Real-World Applications of Evolvable Hardware                                                                                                                                                |

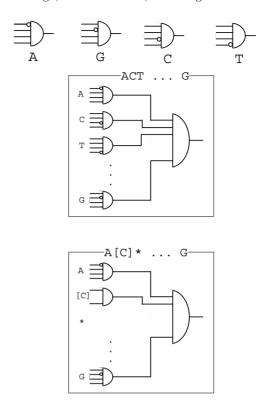

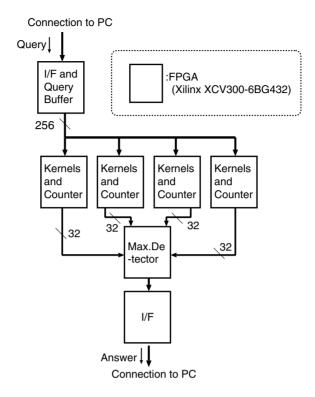

| Gene Finding Using Evolvable Reasoning Hardware                                                                                                                                                                                  |

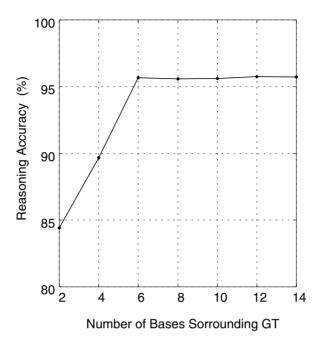

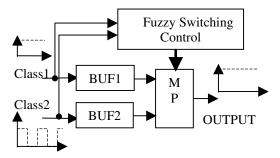

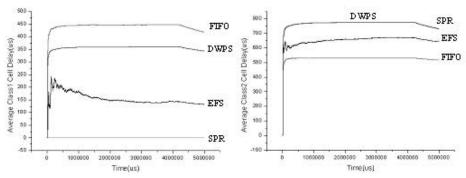

| Evolvable Fuzzy System for ATM Cell Scheduling                                                                                                                                                                                   |

| Evolution of Digital Circuits                                                                                                                                                                                                    |

| Synthesis of Boolean Functions Using Information Theory                                                                                                                                                                          |

| Evolving Multiplier Circuits by Training Set and Training Vector Partitioning                                                                                                                                                    |

| Evolution of Self-diagnosing Hardware                                                                                                                                                                                            |

| Hardware Challenges                                                                         |

|---------------------------------------------------------------------------------------------|

| Routing of Embryonic Arrays Using Genetic Algorithms                                        |

| Exploiting Auto-adaptive $\mu$ GP for Highly Effective Test Programs Generation             |

| Speeding up Hardware Evolution:  A Coprocessor for Evolutionary Algorithms                  |

| Applications 2                                                                              |

| Automatic Evolution of Signal Separators  Using Reconfigurable Hardware                     |

| Distributed Control in Self-reconfigurable Robots                                           |

| Co-evolving Complex Robot Behavior                                                          |

| Evolutionary Hardware                                                                       |

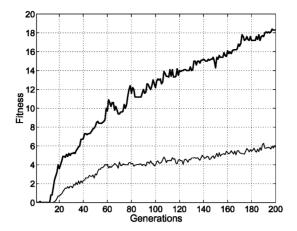

| Evolving Reinforcement Learning-Like Abilities for Robots                                   |

| Evolving Image Processing Operations for an Evolvable Hardware Environment                  |

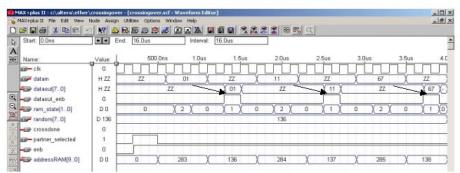

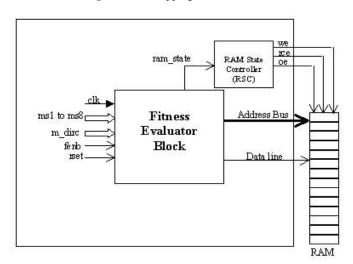

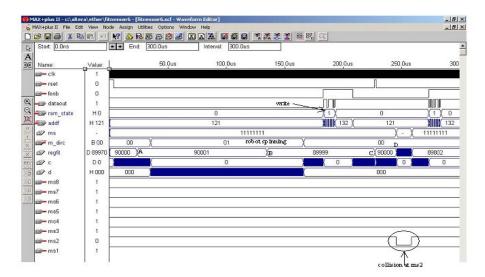

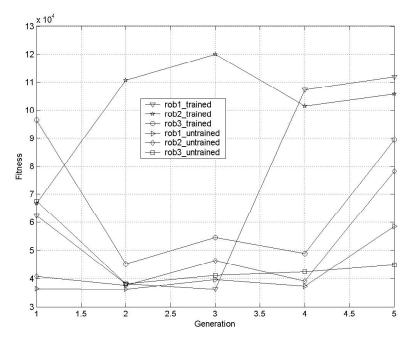

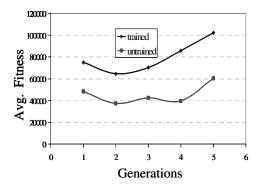

| Hardware Implementation of a Genetic Controller and Effects of Training on Evolution        |

| Neural Systems                                                                              |

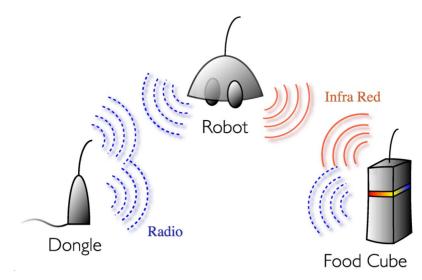

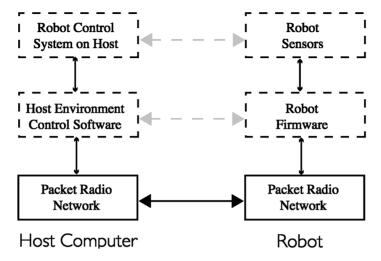

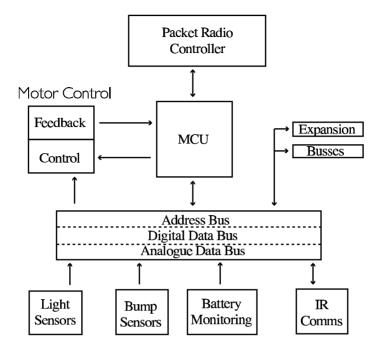

| Real World Hardware Evolution:  A Mobile Platform for Sensor Evolution                      |

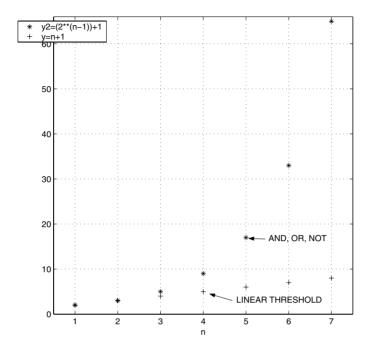

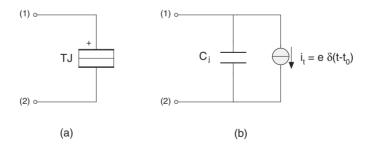

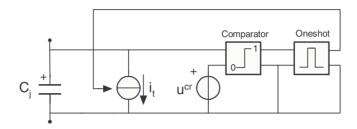

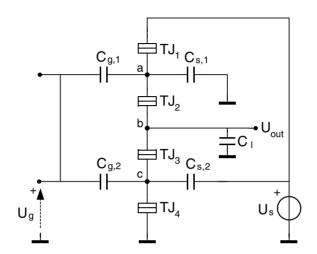

| Real-Time Reconfigurable Linear Threshold Elements and Some Applications to Neural Hardware |

# XIV Table of Contents

| Simulation of a Neural Node Using SET Technology                                                                         |

|--------------------------------------------------------------------------------------------------------------------------|

| General Purpose Processor Architecture for Modeling Stochastic Biological Neuronal Assemblies                            |

| Logic Design                                                                                                             |

| Use of Particle Swarm Optimization to  Design Combinational Logic Circuits                                               |

| A Note on Designing Logical Circuits Using SAT                                                                           |

| Evolutionary Strategies                                                                                                  |

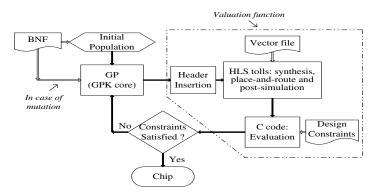

| Using Genetic Programming to Generate Protocol Adaptors for Interprocess Communication                                   |

| Using Genetic Programming and High Level Synthesis to Design Optimized Datapath                                          |

| The Effect of the Bulge Loop upon the Hybridization Process in DNA Computing                                             |

| Quantum versus Evolutionary Systems. Total versus Sampled Search 457<br>Hugo de Garis, Amit Gaur, and Ravichandra Sriram |

| Author Index                                                                                                             |

# On Fireflies, Cellular Systems, and Evolware

Christof Teuscher<sup>1</sup> and Mathieu S. Capcarrere<sup>2</sup>

Logic Systems Laboratory, Swiss Federal Institute of Technology, CH-1015 Lausanne, Switzerland christof@teuscher.ch, http://lslwww.epfl.ch

Computer Science Institute, Collège Propédeutique, University of Lausanne CH-1015 Lausanne, Switzerland

mathieu.capcarrere@philo.unil.ch, http://www-iis.unil.ch/~mcapcarr

Abstract. Many observers have marveled at the beauty of the synchronous flashing of fireflies that has an almost hypnotic effect. In this paper we consider the issue of evolving two-dimensional cellular automata as well as random boolean networks to solve the firefly synchronization task. The task was successfully solved by means of cellular programming based co-evolution performing computations in a completely local manner, each cell having access only to its immediate neighbor's states. An FPGA-based *Evolware* implementation on the BioWall's cellular tissue and different other simulations show that the approach is very efficient and easily implementable in hardware.

#### 1 Introduction

The mutual synchronization of oscillators – a both surprising and interesting phenomenon – in living things and nature is ubiquitous (see for example [12]): dancing (natural response to music), pacemaker cells in the heart, the circadian clock of multicellular organisms (consists of multiple autonomous single-cell oscillators) [31], the nervous system that controls rhythmic behavior such as breathing, running and chewing, synchronous flashing of fireflies, choruses of cicadas or crickets [32], etc.

An oscillator can be defined in a loosely manner as a system that executes a periodic behavior. The pendulum is probably the best example of a periodic behavior in space and time. Electronic circuits offer many different types of oscillators that produce an output signal of a specific frequency. Often, a very stable mechanical oscillator, such as a specially prepared quartz crystal, may be coupled to an electronic oscillator to enhance its frequency stability.

Once the behavior of a single oscillator is understood, the more complex behavior of coupled oscillators can be investigated, although the equations governing their behavior usually become quickly intractable. Strogarz and Stewart [29] write that the most familiar mode of organization for coupled oscillators is synchrony. "One of the most spectacular examples of this kind of coupling can be seen along the tidal rivers of Malaysia, Thailand and New Guinea, where thousands of male fireflies gather together in trees at night and flash on and off

in unison in an attempt to attract the females that cruise overhead. When the males arrive at dusk, their flickerings are uncoordinated. As the night deepens, pockets of synchrony begin to emerge and grow. Eventually whole trees pulsate in a silent, hypnotic concert that continues for hours" [29]. Synchronization in living things usually emerges spontaneously and through cooperative behavior: if a few individuals happen to synchronize, they tend to exert stronger influence on their common neighbors. See Buck and Buck [2] for a review of various theories and information about synchronous fireflies.

Another well known example is the synchronization of menstrual cycles among women friends or roommates [20]. There exist various ideas about the mechanism of synchronization, but an experiment in 1980 has shown that it might have something to do with sweat [24].

In this paper, we concentrate on the two-dimensional firefly synchronization task for non-uniform CAs (each automaton may have a different rule) and random boolean networks. The two-dimensional version of the task is in principle similar to the one-dimensional version, although the speed of synchronization is in general much faster.

The organization of the paper is as follows: Section 2 presents the synchronization task for synchronous cellular automata. Asynchronous automata are presented in Section 3. Section 4.1 briefly presents some measures that allow a better comparison of the experiments. A hardware-based implementation of the firefly synchronization task on the BioWall's cellular tissue is presented in Section 4.2. The CA implemented on the BioWall uses co-evolution in a completely local manner, each cell having access only to its immediate neighbors' states, to find a solution to the task. Section 4.3 presents an alternative to the synchronous application of the genetic algorithms to each cell: the algorithm works asynchronously. Finally, Section 4.4 successfully applies the co-evolutionary approach to random boolean networks (RBN). Section 5 concludes the paper.

# 2 The Synchronization Task for Synchronous Cellular Automata

The one-dimensional synchronization task for synchronous CA was introduced by Das  $et\ al.$  [9] and studied among others by Hordijk [14] and Sipper [27]. In this task the two-state one-dimensional CA, given any initial configuration, must reach a final configuration, within M time steps, that oscillates between all 0s and all 1s on successive time steps. The whole automaton is then globally synchronized. Synchronization comprises a non-trivial computation for a small-radius CA: all cells must coordinate with all the other cells while having only a very local view of its neighbors. The existence of the global clock, though not without consequences as we will see later, should not lure us into thinking that the task is straightforward. Obviously, the fact that the whole computation should only occur within a two-state machine prevents any counting.

In this paper, we concentrate on the two-dimensional version of the task for non-uniform CAs and random boolean networks. The two-dimensional ver-

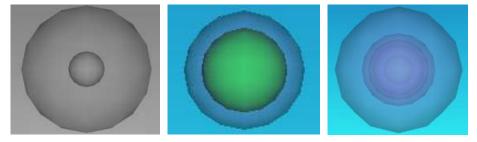

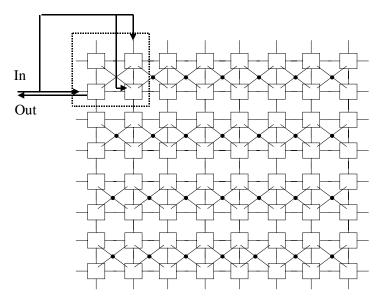

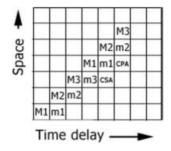

Fig. 1. The two-dimensional synchronization task for synchronous CA. Source: [27].

sion of the task, see Figure 1, is identical to the one-dimensional version except that the necessary number of time steps granted to synchronize is not any more in the order of N, the number of cells in the automaton, but in the order of n+m where n,m are the size of each side of the CA. Thereby, the speed of synchronization is much faster. Non-uniform CAs are CAs where each automaton may have a different rule.

Obviously, in the non-uniform case there is an immediate solution consisting of a unique 'master' rule, alternating between '0' and '1', whatever the neighborhood, and all other cells being its 'slave' and alternating according to its right or up neighbor state only. However, Sipper [27] used non-uniform CAs to find perfect synchronizing CAs only by means of evolution. It appeared that this "basic" solution was never found by evolution and, in fact, the "master" or "blind" rule 10101010 (rule 170) in one dimension, was never part of the evolved solutions. This is simply due to the fact that this rule has to be unique for the solution to be perfect, which is contradictory to the natural tendency of the evolutionary algorithm used, as we demonstrated in [3]. In this paper, we only use evolved solutions to this task.

# 3 Asynchronous Cellular Automata

In the preceding section the CA model is synchronous as is traditionally the case. But this feature is far from being realistic from a biological point of view as well as from a computational point of view. As for the former, it is quite evident that there is no accurate global synchronization in nature. As for the latter, it turns out to be impossible to maintain a large network of automata globally synchronous in practice. Besides, it is interesting to try to delineate what part of the computation relies on the synchrony constraint.

Ingerson and Buwel [15] compared the different dynamical behavior of synchronous and asynchronous CAs; they argued that some of the apparent selforganization of CAs is an artifact of the synchronization of the clocks. Wolfram [33] noted that asynchronous updating makes it more difficult for information to propagate through the CA and that, furthermore, such CAs may be harder to analyze. Asynchronous CAs have also been discussed from a problemsolving and/or Artificial Life standpoint in references [22, 1, 25, 16, 13, 28]. All these works devoted to asynchronous cellular automata only concentrated on the study of the effects but not on correcting asynchrony or dealing with it. From a theoretical computer science perspective, Zielonka [34, 35] introduced the concept of asynchronous cellular automata. Though the question attracted quite some interest [18, 23, 8], the essential idea behind them was to prove that they were "equivalent" to synchronous CA in the sense that, for instance, they recognize the same trace languages or could decide emptiness. From these two fields, we thus knew that asynchronous CA are potentially as powerful as synchronous CA, computationally speaking<sup>1</sup>, and, nevertheless, that most of the effects observed in the synchronous case are artifacts of the global clock.

In [5,4] we proposed asynchronous CAs exhibiting the same behavior as synchronous CAs through both design and evolution. The main idea behind these models was that time is part of the information contained in a CA configuration. Hence suppressing the global clock constraint is equivalent to suppressing information. Thereby, and quite naturally, if we are to maintain the capability of the CA, then we must compensate for that loss of information by adding extra states. As shown then, it is possible to design a CA with  $3*q^2$  states working asynchronously which simulates perfectly a given q-state CA. Tolerating some loss of information, we have shown that it was possible to evolve self-correcting 4-state CA to do the synchronization task under low asynchrony.

As Gacs [10,11] reminds us, asynchrony may be considered as a special case of fault-tolerance. However, even though this consideration is nice in its generalization (i.e., a fault-tolerant CA is also asynchronous), it eschews a lot of potential optimization.

# 4 Implementations and Experiments

# 4.1 Genotypic Measures for Non-uniform CAs

To better compare the different simulations and implementations, we define a number of metrics (some of them adapted from [3]).

Let's first define N to be the total number of cells. We have N = n\*m where m, n are the length of the sides of the two-dimensional CA considered. We can now define the frequency of transitions,  $\nu$ , as the number of borders between homogeneous blocks of cells having the same genotype, divided by the number of distinct couples of adjacent cells. Adjency is here taken along the neighborhood

<sup>&</sup>lt;sup>1</sup> In the traditional sense, not in the sense of visual computation.

used, that is the von Neumann neighborhood. Thus  $\nu$  is the probability that two adjacent cells have a different rule (Equation 1).

$$\nu = \frac{1}{2(n*m)} \sum_{i=1}^{n} \sum_{j=1}^{m} \left[ R_i, j \neq R_{(i+1 \bmod n, j)} + R_i, j \neq R_{(i,j+1 \bmod m)} \right]$$

(1)

can also define a more global measure of the diversity of the different genotypes encountered, an entropy, H (Equation 2).

$$H = \sum_{r \in \Gamma} q(r) * log\left(\frac{1}{q(r)}\right)$$

(2)

where  $\Gamma$  is the set of all possible genotypes (rules), and q(r) is the global proportion of the genotype (rule) r in the cellular automata. Obviously, H takes on values in the interval  $[0, \log n]$  and attains its maximum,  $H(x) = \log n$ , when x comprises n different genotypes. H is usually normalized to take values in the interval [0, 1].

#### 4.2 Firefly Hardware

Fireflies synchronize according to the "pulse coupled" system [21], i.e., they interact only when one sees the sudden flash of another. The firefly then shifts its rhythm accordingly. "Pulse coupling is difficult to handle mathematically because it introduces discontinuous behavior into the otherwise continuous model and so stymies most of the standard mathematical techniques" [29]. Mathematicians have turned to the theory of symmetry breaking to tackle the complex problems that arise when identical oscillators are coupled. Computer scientists, on the other hand, often use cellular automata, irregular networks and grid arrays or more complex agent-based models to analyze the behavior of interacting elements.

In 1997, the Logic Systems Laboratory presented an evolving hardware system called *Firefly* [26] that successfully solved the synchronization task in one dimension using cellular programming based co-evolution. The novelty of Firefly was that it operates with no reference to an external device (such as a computer that carries out genetic operators) thereby exhibiting online autonomous evolution.

Recently, the synchronization task in two dimensions has successfully been evolved on the BioWall's 3200 FPGAs. The BioWall [30] is a giant reconfigurable computing tissue developed to implement machines according to the principles of the *Embryonics* (embryonic electronics) project [19]. The BioWall's size and features are designed for public exhibition, but at the same time it represents an invaluable research tool, particularly since its complete programmability and cellular structure are extremely well adapted to the implementation of many different kinds of bio-inspired systems. The implementation on the BioWall consists of a two-state, non-uniform CA, in which each cell (i.e., each FPGA of the BioWall) may contain a different rule. The cells rule tables are encoded as a

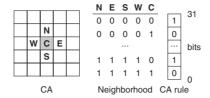

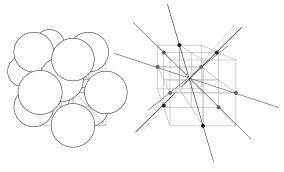

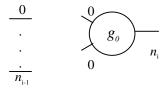

Fig. 2. Von Neumann neighborhood of our two-dimensional CA and cell rule encoding.

bit-string, known as the genome, that has a length of  $2^5 = 32$  bits for our 2D CA since the binary CA has a neighborhood of 5 (see also Figure 2).

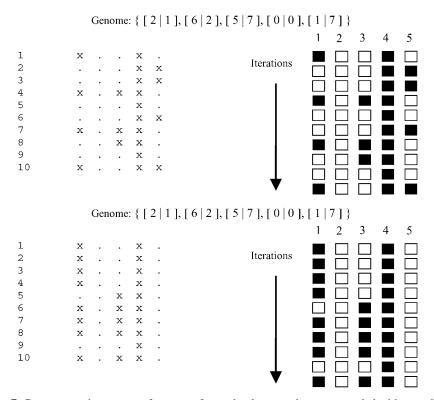

Rather than to employ a population of evolving CAs, our algorithm (see Algorithm 1) evolves a single, non-uniform CA of the size of the entire BioWall (one cell of the CA in each unit of the BioWall, that is, 3200 cells), whose rules are initialized at random. Initial configurations are then randomly generated and for each configuration the CA is run for M time steps (M has been set to 2(n+m)=2(160+20)=360, where n,m are the size of each side of the CA). Each cell's fitness is accumulated over C (C has been set to 300) initial configurations. The (local) fitness score for the synchronization task is assigned to each cell by considering the last four time steps (M+1 to M+4): if the sequence of states over these steps is precisely 0-1-0-1, the cell's fitness score is 1, otherwise this score is 0.

After every C configurations the rules are evolved through crossover and mutation. This evolutionary process is performed in a completely local manner, that is, genetic operators are applied only between directly connected cells. Unlike standard genetic algorithms, where a population of independent problem solutions globally evolves, our approach involves a grid of rules that co-evolves locally. The CA implemented on the BioWall performs computations in a completely local manner, each cell having access to its immediate neighbors' states only. In addition, the evolutionary process is also completely local, since the application of the genetic operators as well as the fitness assignment occurs locally. Using the above-described cellular programming approach (see also Algorithm 1) on the BioWall, we have shown that a non-uniform CA of radius 1 can be evolved to successfully solve the synchronization task. In addition, once a set of successful rules has been found, our machine allows the state of each CA cell to be changed by pressing on its membrane. The user can then observe how the machine synchronizes the 3200 cells.

In contrast to the original Firefly machine [26], which used a slightly simplified algorithm to facilitate the implementation, the BioWall implements exactly the algorithm as described above. The BioWall implementation, however, contains no global synchronization detector, therefore, it is not 100% guaranteed that the CA always synchronizes perfectly (i.e., for any initial configuration). Each cell contains a pseudo-random generator, realized by means of a linear feedback shift register, to initialize randomly the cell's state and its rule table. The register receives an initial random seed from an external PC that also con-

# **Algorithm 1** Cellular programming pseudo-code for the synchronization of a two-dimensional cellular automaton

```

for each cell i in CA [in parallel] do

Initialize rule table of cell i randomly

f_i = 0 [fitness value]

end for

c = 0 [initial configurations counter]

while not done do

Generate a random initial configuration

Run CA on initial configuration for M = 2(m+n) time steps

for each cell i in CA [in parallel] do

if cell i is in the correct final state then

f_i = f_i + 1

end if

end for

c = c + 1

if c \mod C = 0 [evolve every C configurations] then

for each cell i [in parallel] do

Compute nf_i(c) [number of fitter neighbors]

if n f_i(c) = 0 then

Rule i is left unchanged

else if nf_i = 1 then

Replace rule i with the fitter neighboring rule, followed by mutation

else if n f_i > 1 then

Replace rule i with the crossover of the two fittest neighboring rules (ran-

domly chosen, if equal fitness), followed by mutation

end if

f_i = 0

end for

end if

end while

```

figures the FPGAs. The actual implementation easily fits into a Xilinx Spartan XCS10XL FPGA.

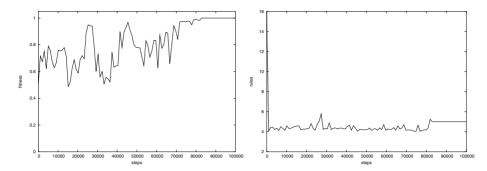

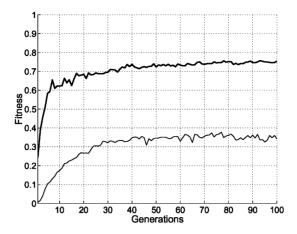

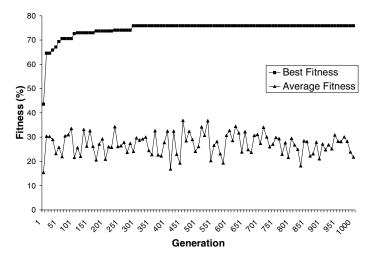

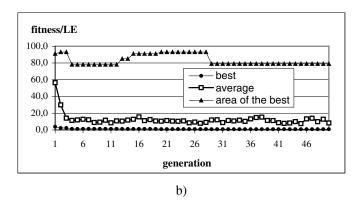

As an example, Figure 3 shows the evolution of the fitness as well as the number of rules in function of the number of evolutionary phases for a small  $4 \times 4$  cell CA (toroidal). A solution that perfectly synchronizes the 16 cells from any initial configuration (there are  $2^{16} = 65536$ ) has been found with the following five rules:

| 99ea2e68 | 81f2a5fa | fe7aeb98 | bf82fa06 |

|----------|----------|----------|----------|

| 99ea2e68 | 81f2a5fa | fe7aeb98 | bf82fa06 |

| 99ea2e68 | 81f2a5fa | fe7aeb98 | bf82fa06 |

| 99e82e68 | 81f2a5fa | fe7aeb98 | bf82fa06 |

As stated in Section 2, there is a trivial solution with two rules (one cell being the 'master' and all the other cells being 'slaves'), but it is very unlikely that this configuration is found by evolution since this rule has to be unique for

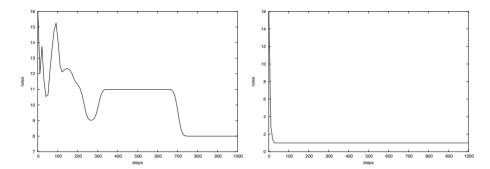

**Fig. 3.** The CA's fitness (on the left) and the number of different rules (on the right) of a small  $4 \times 4$  cell CA (means over several runs). The CA successfully synchronizes for any initial configuration using five different rules.

Algorithm 2 Cellular programming pseudo-code for the synchronization of a two-dimensional cellular automaton using asynchronous co-evolution

```

for each cell i in CA [in parallel] do

Initialize rule table of cell i randomly

end for

while not done do

Generate a random initial configuration

for D steps do

Run CA on initial configuration for T time steps

Choose a cell i at random

Compute fitness f_i and fitness of adjacent cells

Apply GA to cell i [crossover and mutation]

end for

end while

```

the solution to be perfect. The above example has a  $\nu$  of 0.563, the entropy H is 0.562.

#### 4.3 Asynchronous Co-evolution

In the previous section we described the co-evolution of a synchronous CA where the genetic algorithm in each cell is synchronized by means of a global signal: all cells evaluated the fitness at the same time, replaced the rules at the same time, etc. It would obviously be interesting to use some kind of 'asynchronous' co-evolution where cells still operate synchronously, but where the genetic algorithm operates asynchronously and randomly in time. This would allow to remove the GA's global synchronization signal.

We used the method as shown in Algorithm 2.

Our simulations (with  $T=10N,\,D=N$ ) have revealed that the CA is still able to synchronize perfectly, although more different rules are required and synchronization seems slower in general. Evolution found eight different rules for

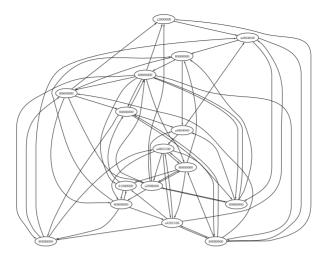

Fig. 4. A random graph with 4 incoming links per node/cell. The eight rules that allow to perfectly synchronize any initial configuration are written on the nodes.

the example of the previous section. Naturally, the probability that two adjacent cells have a different rule was higher:  $\nu = 0.969$ . The entropy H was 0.938.

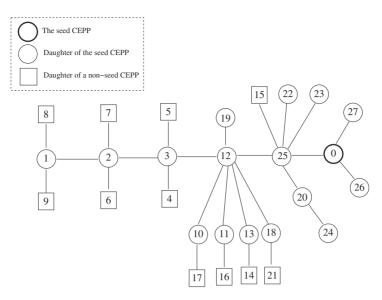

#### 4.4 The Synchronization Task for Random Boolean Networks

Solving the synchronization task on a completely regular grid abstracts from the original firefly synchronization task in nature and it would thus be more interesting and biologically plausible to use a random graph. To avoid problems during crossover between rules having different lengths, the number of incoming links per node/cell was held constant. Figure 4 shows a random graph with four incoming links per node. Using Stuart Kauffman's terminology (see for example [17]), the graph is a N=16, K=4 random boolean network. In this context, K specifies the exact number of inputs per node.

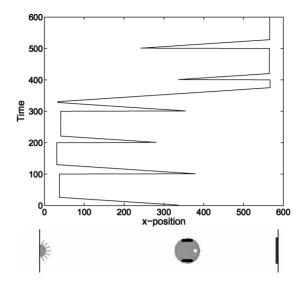

Using Algorithm 1, our co-evolutionary approach was able to find a perfect solution using eight different rules ( $\nu=0.859,\ H=0.652$ ) for the K=4 random boolean network (RBN) of Figure 4. Figure 5 shows the evolution of the number of rules for a K=4 (on the left) and for a K=2 RBN (on the right). It is astonishing that one rule is in general sufficient for the K=2 network ( $\nu=0,\ H=0$ ). Further investigations would be needed, but it almost certainly has something to do with Kauffman's findings that the most highly organized behavior appeared to occur in networks where each node receives inputs from two other nodes (K=2). It turned out that Kauffman's networks exhibit three major regimes of behavior: ordered (solid), complex (liquid), and chaotic (gas). The most complex and interesting dynamics correspond to the liquid interface, the boundary between order and chaos. In the ordered regime, little computation can occur. In the chaotic phase, dynamics are too disordered to be useful.

**Fig. 5.** The number of different rules (on the left) of a K=4 random boolean network (RBN) and of a K=2 RBN (on the right). The K=2 network synchronizes with one rule only, the k=4 network with eight rules.

#### 5 Conclusion and Future Work

In this paper we considered the issue of evolving two-dimensional cellular automata as well as random boolean networks to solve the firefly synchronization task. The task has been solved using a co-evolutionary genetic algorithm that performs computations in a completely local manner, each cell having access to its immediate neighbors' states only.

The FPGA-based implementation on the BioWall's cellular tissue exhibits complete online co-evolution using local interactions only between neighboring cells. Besides the global clock signals, no other global signal is needed.

Our experiments have shown that the cellular programming based approach is very efficient, easily finds a solution for classical two-dimensional cellular automata as well as for random boolean networks, and is easily implementable on cellular hardware (e.g. FPGAs or arrays of FPGAs) since there are – except the global clock signal – no other global signals needed.

Future work will be focused on the firefly synchronization of completely asynchronous cellular automata and of random boolean networks having a different number of inputs for each cell. This would allow to remove all global signals and to use local clocks only, which would be an important additional advantage for Evolware implementations. Another focus point will be the synchronization of imperfect (lossy) 2D CAs and networks similar to the recent work of Challet and Johnson [6] (see also [7]) who have shown how imprecise clocks can keep good time by working together.

# Acknowledgments

We are grateful to Philippe Raoult, Hans Jäckle, and Pierre-André Mudry for their help.

#### References

- H. Bersini and V. Detours. Asynchrony induces stability in cellular automata based models. In R.A. Brooks and P. Maes, editors, *Proceedings of the Artificial Life IV* conference, pages 382–387, Cambridge, MA, 1994. MIT Press.

- J. Buck and E. Buck. Synchronous fireflies. Scientific American, 234:74–85, May 1976.

- 3. M. S. Capcarrere, A. Tettamanzi, M. Tomassini, and M. Sipper. Statistical study of a class of cellular evolutionary algorithms. *Evolutionary Computation*, 7(3):255–274, 1998.

- M. S. Capcarrere. Cellular Automata and Other Cellular Systems: Design & Evolution. PhD Thesis No 2541, Swiss Federal Institute of Technology, Lausanne, 2002.

- M. S. Capcarrere. Evolution of asynchronous cellular automata. In J. J. Merelo, A. Panagiotis, and H.-G. Beyer, editors, Parallel Problem Solving from Nature -PPSN VII 7th International Conference, Granada, Spain, September 7-11, 2002, Proceedings. Springer-Verlag, 2002.

- 6. D. Challet and N. F. Johnson. Optimal combinations of imperfect components. *Physical Review Letters*, 89(2):028701–1–028701–4, July 8 2002.

- 7. A. Cho. Collective effort makes the good times roll. Science, 297:33, July 5 2002.

- R. Cori, Y. Métivier, and W. Zielonka. Asynchronous mappings and asynchronous cellular automata. *Information and Computation*, 106:159–202, 1993.

- 9. R. Das, J. P. Crutchfield, M. Mitchell, and J. E. Hanson. Evolving globally synchronized cellular automata. In L. J. Eshelman, editor, *Proceedings of the Sixth International Conference on Genetic Algorithms*, pages 336–343, San Francisco, CA, 1995. Morgan Kaufmann.

- P. Gács. Self-correcting two-dimensionnal arrays. In Silvio Micali, editor, Randomness in computation, volume 5 of Advances in Computing Research, pages 223–326, Greenwich, Conn, 1989. JAI Press.

- 11. P. Gács. Reliable cellular automata with self-organization. In *Proceedings of the* 38th IEEE Symposium on the Foundation of Computer Science, pages 90–99, 1997.

- L. Glass and M. C. Mackey. From Clocks to Chaos: The Rhythms of Life. Princeton University Press, 1988.

- H. Hartman and Gérard Y. Vichniac. Inhomogeneous cellular automata (inca).

In E. Bienenstock et al., editor, Disordered Systems and Biological Organization, volume F 20, pages 53–57. Springer-Verlag, Berlin, 1986.

- W. Hordijk. The structure of the synchonizing-CA landscape. Technical Report 96-10-078, Santa Fe Institute, Santa Fe, NM (USA), 1996.

- T. E. Ingerson and R. L. Buvel. Structures in asynchronous cellular automata. *Physica D*, 10:59–68, 1984.

- Y. Kanada. Asynchronous 1D cellular automata and the effects of fluctuation and randomness. In R. A. Brooks and P. Maes, editors, ALife IV: Proceedings of the Fourth Conference on Artificial Life, page Poster, Cambridge, MA, 1994. MIT Press.

- 17. S. A. Kauffman. The Origins of Order: Self-Organization and Selection in Evolution. Oxford University Press, New York; Oxford, 1993.

- D. Kuske. Emptiness is decidable for asynchronous cellular machines. In C. Palamidessi, editor, CONCUR 2000, Lecture Notes in Computer Science, LNCS 1877, pages 536–551, Berlin, 2000.

- D. Mange, M. Sipper, A. Stauffer, and G. Tempesti. Toward robust integrated circuits: The embryonics approach. *Proceedings of the IEEE*, 88(4):516–540, April 2000.

- M. K. McClintock. Menstrual synchrony and suppression. Nature, 229:244–245, 1971.

- 21. R. E. Mirollo and S. H. Strogatz. Synchronization of pulse-coupled biological oscillators. *SIAM Journal on Applied Mathematics*, 50(6):1645–1662, December 1990.

- M. A. Nowak, S. Bonhoeffer, and R. M. May. Spatial games and the maintenance of cooperation. Proceedings of the National Academic of Sciences USA, 91:4877–4881, May 1994.

- 23. G. Pighizzini. Asynchronous automata versus asynchronous cellular automata. Theoretical Computer Science, 132:179–207, 1994.

- 24. M. J. Russel, M. G. Switz, and K. Thompson. Olfactory influences on the human menstrual cycle. *Pharmacology Biochemistry and Behavior*, 13:737–738, 1980.

- B. Schönfisch and A. de Roos. Synchronous and asynchronous updating in spatially distributed systems. BioSystems, 51:123–143, 1999.

- M. Sipper, M. Goeke, D. Mange, A. Stauffer, E. Sanchez, and M. Tomassini. The firefly machine: Online evolware. In *Proceedings of the 1997 IEEE International* Conference on Evolutionary Computation (ICEC'97), pages 181–186. IEEE, 1997.

- 27. M. Sipper. Evolution of Parallel Cellular Machines: The Cellular Programming Approach. Springer-Verlag, Heidelberg, 1997.

- 28. R. W. Stark. Dynamics for fundamental problem of biological information processing. *International Journal of Artificial Intelligence Tools*, 4(4):471–488, 1995.

- 29. S. H. Strogatz and I. Stewart. Coupled oscillators and biological synchronization. *Scientific American*, 269:68–75, December 1983.

- 30. G. Tempesti, D. Mange, A. Stauffer, and C. Teuscher. The Biowall: An electronic tissue for prototyping bio-inspired systems. In A. Stoica, J. Lohn, R. Katz, D. Keymeulen, and R. S. Zebulum, editors, *Proceedings of the 2002 NASA/DoD Conference on Evolvable Hardware*, pages 221–230. IEEE Computer Society, Los Alamitos, CA, 2002.

- H. R. Ueda, K. Hirose, and M. Iino. Intercellular coupling mechanism for synchronized and noise-resistant circadian oscillators. *Journal of Theoretical Biology*, 216:501–512, 2002.

- T. J. Walker. Acoustic synchrony: Two mechanisms in the snowy tree cricket. Science, 166:891–894, 1969.

- 33. S. Wolfram. Approaches to complexity engineering. Physica D, 22:385–399, 1986.

- 34. W. Zielonka. Notes on finite asynchronous automata. Informatique théorique et Applications/Theoretical Infomatics and Applications, 21(2):99–135, 1987.

- 35. W. Zielonka. Safe executions of recognizable trace languages by asynchronous automata. In Albert R. Meyer and Michael A. Taitslin, editors, *Logic at Botik'89*, Lecture Notes in Computer Science, LNCS 363, pages 278–289, Berlin, 1989. Springer-Verlag.

# A Comparison of Different Circuit Representations for Evolutionary Analog Circuit Design

Lyudmilla Zinchenko<sup>2</sup>, Heinz Mühlenbein<sup>1</sup>, Victor Kureichik<sup>2</sup>, and Thilo Mahnig<sup>1</sup>

<sup>1</sup>FhG-AiS Schloss Birlinghoven 53754 Sankt – Augustin Germany {muehlenbein, mahnig}@gmd.de

<sup>2</sup>Taganrog State University of Radio Engineering, l. Nekrasovsky, 44, GSP-17A, Taganrog, 347928, Russia {kur,toe}@tsure.ru

Ph. +7-8634-371-694

**Abstract.** Evolvable hardware represents an emerging field in which evolutionary design has recently produced promising results. However, the choice of effective circuit representation is inexplicit. In this paper, we compare different circuit representations for evolutionary analog circuit design. The results indicate that the design quality is better for the element-list circuit representation.

#### 1 Introduction

Circuit design is a difficult problem because of huge design space dimensions [1]. Different circuits are generated by a variation of parameters and topologies. Mainly they are useless, while the small part of them corresponds to a design goal. An effective search in such large complex spaces is impossible without smart tools [5]. One of the approaches to circuit design is a restriction of design space by means of expert knowledge. However, an expert circuit designer uses the part of possible circuit solutions that have been found by chance or by a search within tiny regions.

Recently, automated analog circuit design techniques have been proposed. Their advantage is a search within the whole space, but it requires large computational efforts. There are several approaches to a reduction of design space by means of macromodelling, symbolic analysis etc. [3]. However, the application of evolutionary algorithms for circuit design seems the most attractive approach, which allows us to obtain novel circuit solutions. Many positive results have been published [1-15]. However, the choice of the best structure of evolutionary design is unclear. Circuit representation, fitness evaluation technique, and search method have to be chosen for effective evolutionary circuit design carefully. However, their choice is inexplicit in practice.

In this paper we aim to compare different circuit representations for static fitness schedule and distribution algorithms. Univariate and bivariate distribution algorithms use estimations of the probability. Hence, a reasonable choice of circuit representation has a profound result for effective circuit design. We compare the effectiveness of branch-list circuit representation and element-list circuit representation for univariate algorithms. We use lowpass filter benchmark.

The remainder of the paper is organized as follows. Section 2 summaries briefly recent results obtained for evolutionary circuit design. Section 3 elaborates on the

circuit representations. The experimental setup and results are presented in Sections 4 and 5. We discuss the results in Section 6.

# 2 Approaches to Evolutionary Circuit Design

Evolutionary algorithms are used both for digital circuit design and analog circuit design [1]. Circuit representation, fitness evaluation technique, and search algorithms are crucial ingredients of evolutionary circuit design. In this paper, we restrict our research to analog circuit design, although there are the same problems for digital circuit design as well.

A correct circuit representation is the base for effective design. There are many approaches to circuit description. Tree representation is used by the growing technique [8], which allows us to obtain a sequence of circuits by an addition or a deletion of circuit elements. The deficiencies of the approach are circuits of illegal topologies that are generated at each step. Analysis of useless solutions requires computational efforts, while solutions have the right topology only. A generation of certain topologies using cc-bot instructions restricts the design space [4]. This limitation has both advantages and deficiencies. The computation efforts are reduced, whilst a circuit variety is restricted as well. The matrix representation [11] requires preliminary knowledge. It should be noted that it is used for fixed circuit sizes only. The integer representation, which is based on the linear string, has been used effectively [7, 11].

The complexity of evolutionary design is defined by the ruggedness of fitness landscape. Some investigations of fitness landscape changes have been performed. Dynamic fitness schedules change the fitness landscape [6], but their deficiency is a varying gradient of the fitness function landscape. For the following generations the information obtained is false. The fitness evaluation technique [13] varies for small and large circuits by means of penalty coefficients. Therefore, more efficient solutions are selected at each step.

Note that the right choice of search algorithm represents the most important decision for effective design. There are many publications that represent the applications of genetic programming, genetic algorithms, and evolutionary strategies for circuit design [8 - 10]. Specific mutation operators for analog circuit design have been used in [12]. Some researchers combine genetic search and annealing optimisation [3], genetic algorithms and Davidon-Fletcher-Powell optimisation method [14]. The positive results have been obtained for the hardware immune system [2]. Recently, ant colony algorithm has been used for analog circuit design successfully [15]. Our focus is on the application of probabilistic evolutionary models. The Estimation of Distribution Algorithms EDA has been proposed by Mühlenbein and Paaß [16] as an extension of genetic algorithms. Instead of performing recombination of strings, EDA generates new points according to the probability distribution defined by the selected points. In [17] Mühlenbein showed that genetic algorithms can be approximated by an algorithm using univariate marginal distributions only (UMDA). UMDA is an evolutionary algorithm, which combines mutation and recombination by means of distribution. The distribution is estimated from a set of selected points. It is used then to generate new points for the next generation. It should be noted that we use truncation selection because of its simplicity. Some experimental results of the distribution algorithms application for several test functions have been published in [18]. Recently, we have proposed the dynamic coding, the hierarchy circuit representation, and the application of UMDA for analog circuit design that allow us to use topological and parametrical search simultaneously [19]. Observe that the hierarchical genotype structure reduces the search space without the restriction of circuit variety. In order to improve design abilities, mutation has been introduced into UMDA by a concept called Bayesian prior [18]. The choice of hyperparameter r has been considered for test functions [18]. We have improved the effectiveness of circuit design by means of mutation too [20]. UMDA with Bayesian prior is able to overcome local minima. Furthermore, we used the experimental research in order to make a reasonable choice of Bayesian prior for analog circuit design [21]. Moreover, we synthesized the circuits that are better than those produced by an expert circuit designer [20, 21].

The probabilistic approach evaluates the direct relation between the genotype and the fitness. In this paper we compare different circuit representations for the application of UMDA for analog circuit design. It should be noted that we restrict our research to the static technique of fitness function evaluation only.

# 3 Circuit Representations

There are many circuit representation techniques for evolutionary circuit design. The hierarchical circuit representation [19 - 21] was chosen as the basis for the investigation for the following reasons. First, as a large number of circuits are needed to evaluate, the search within the whole space will be very slow. Second, the relations between the circuit elements and the circuit parameters cannot be estimated for different elements. Physical nature is different for capacitances and inductances. Therefore, probabilistic models have to be evaluated for capacitance parameters and for inductance parameters separately.

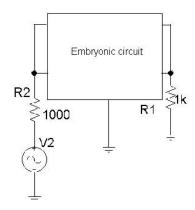

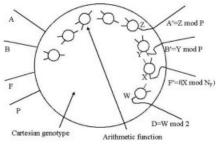

The growing technique is used during the evolutionary design. The embryonic circuit is shown in Fig. 1. The evolutionary process is based on the topology of the complete graph. Adjacency matrix of the *N*-node complete graph is given as follows [22]:

$$A = \begin{cases} a_{ij} = 0 & if \quad i = j \\ a_{ij} = 1 & if \quad i \neq j \end{cases} . \tag{1}$$

First, we specify the boundary limits on the amount of the circuit nodes. Second, each element is determined by its type and parameter. Two bits define the type. Each element can take on 3 different types, namely, switch (0), capacitance (1) and inductance (2). Three bits define a parameter of element. The parameter of switch can take on two fixed values only. We consider that 0 means that a switch is turned off and 1 means that a switch is turned on. Parameters of inductances and capacitances are chosen from the given range. The input of the circuit is always node 1 and the output is node 2. Branch 1 is always series connection of a voltage source and the source resistance. Branch 2 is the load resistance. The circuit being evolved contains (n-2) branches. The amount of the branches is given as follows:

$$n = \sum_{i=0}^{N-1} (N-i).$$

(2)

Fig. 1. The embryonic circuit of two-ports

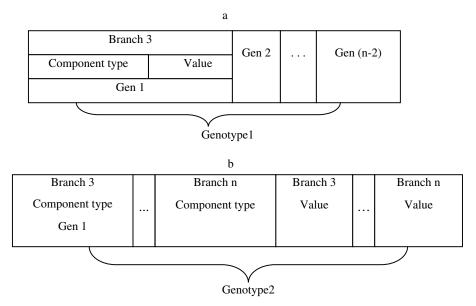

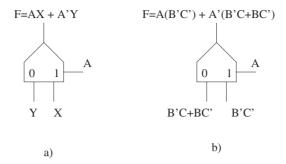

Fig. 2. General structure of the branch circuit representation Genotype1 (a), general structure of the element circuit representation Genotype2 (b)

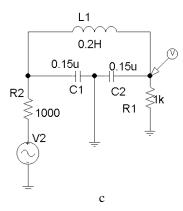

We propose two circuit representations that use the adjacency matrix (1). Figure 2 shows their general structure. Figure 3 illustrates the case of the 3 node topology. Chromosome length is equal to 23. The best circuit is shown in Fig. 3 (c).

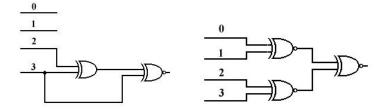

#### 3.1 Branch-List Circuit Representation

The branch-list circuit representation is one of standard circuit representation techniques for evolutionary analog circuit design. A genotype is formed by means of the combination of separate genes for each branch. The circuit representation used is similar to [7, 11, 12, 19]. Briefly, each gene consists of alleles for a type, connecting

nodes and value parameters. The genotype [type, connecting nodes, value parameters] [11, 12], the genotype [connecting nodes, value parameters, type] [7], and the hierarchical genotype [type / value parameters] [19] are possible modifications. Fig.2 (a) shows general structure of the branch-list circuit representation (Genotype1). The description of Genotype1 for the chromosome of length 23 is illustrated in Fig. 3 (a). The correspondent adjacency matrix is given as follows:

$$A = \begin{vmatrix} 0 & 1 & 1 & 1 \\ 1 & 0 & 1 & 1 \\ 1 & 1 & 0 & 1 \\ 1 & 1 & 1 & 0 \end{vmatrix}. \tag{3}$$

| Amount of nodes | Branch 3                           | Branch 4 | Branch 5 | Branch 6 |  |

|-----------------|------------------------------------|----------|----------|----------|--|

| 0 1 1           | 10 011<br>!!!<br>Element parameter | 01101    | 01101    | 00001    |  |

a

| Amount | Element |     |     | Parameter |       |     |     |       |

|--------|---------|-----|-----|-----------|-------|-----|-----|-------|

| of     | В       | В   | В   | В         | В     | В   | В   | В     |

| nodes  | r       | r   | r   | r         | r     | r   | r   | r     |

|        | a       | a   | a   | a         | a     | a   | a   | a     |

|        | n       | n   | n   | n         | n     | n   | n   | n     |

|        | c       | c   | c   | c         | c     | c   | c   | c     |

|        | h       | h   | h   | h         | h     | h   | h   | h     |

|        | 3       | 4   | 5   | 6         | 3     | 4   | 5   | 6     |

|        |         |     |     |           |       |     |     |       |

| 0 1 1  | 10      | 0 1 | 0 1 | 0 0       | 0 1 1 | 101 | 101 | 0 0 1 |

b

**Fig. 3.** The branch circuit representation Genotype1 (a), the element circuit representation Genotype2 (b), and the best circuit (c)

#### 3.2 Element-List Circuit Representation

The element-list circuit representation is a circuit representation modification. It should be noted that topology information is more important for circuit design. Thus, we suppose that a change of circuit representation could improve the effectiveness of evolutionary search. The topological information is concentrated within the first alleles, whilst the rest of genotype holds alleles for the value parameters. Fig. 2 (b) shows general structure of the element - list circuit representation (Genotype2). The description of Genotype2 for the chromosome of length 23 is illustrated in Fig. 3 (b).

The correspondent adjacency matrix is given by (3). Such representation is effective when the ruggedness of the fitness landscape is reduced. Otherwise it is disadvantageous. Fig.3 indicates that the phenotypes are the same ones, whilst the genotypes are different. Hence, the interactions between the alleles are different as well. Therefore, the efficiency of evolutionary design can be changed. In order to determine the deficiencies of different circuit representation it is useful to compare their behaviour.

# 4 Experimental Setup

Maximum stop-band gain (dB)

The circuit design benchmark chosen was the lowpass filter. Such circuits have wide applications, although the design theory is based on some simple circuits. The starting point for the design of a filter is the specification of the frequencies for the filter's pass-band and stop-band. The design of filters with high stop-band attenuation and low pass-band attenuation is hard. It is more difficult to design a lowpass filter with small transitional region between two bands. The input specification for the filter design benchmark is summarized in Table 1. The ratio between signal in the pass-band (1 V) and the maximum acceptable signal in the stop-band (1 mV) is 60 decibels, although there is 2-to-1 ratio between the stop-band frequency and the pass-band frequency. The known design methods generate the desired circuit, although there are some fluctuations in the stop-band and in the pass-band.

| Table 1. Input specifications for the filter design benchmark |        |  |  |  |

|---------------------------------------------------------------|--------|--|--|--|

| Circuit Specifications                                        | Values |  |  |  |

| Minimum number of components                                  | 3      |  |  |  |

| Maximum number of components                                  | 6      |  |  |  |

| Pass-band frequency (Hz)                                      | 1000   |  |  |  |

| Stop-band frequency (Hz)                                      | 2000   |  |  |  |

| Maximum pass-band gain (dB)                                   | 0      |  |  |  |

| Minimum pass-band gain (dB)                                   | -0.26  |  |  |  |

| Minimum pass-band gain (dB)                                   | -0.26  |  |  |  |

-60

In order to reduce computational efforts the fitness is evaluated by means of equation-based method [20]. The numerical frequency response evaluation and the modified nodal method are used. The fitness function evaluation technique used is similar to those described in [20, 21]. The fitness is evaluated in terms of the sum of the absolute weighted difference between the actual output voltage and the target one. These error values were summed across evaluation points *Nc* for the evaluation of the fitness

$$F = \sum_{i=0}^{Nc} W[d(f_i), f_i)] d(f_i)$$

(4)

$$d(f) = \left| U_{goal}(f) - U_{out}(f) \right| \tag{5}$$

$$W[d(f), f] = \begin{cases} 1 & \text{if } d(f) \le 0.03, f \le 1000 \text{ Hz}, \\ 10 & \text{if } d(f) \ge 0.03, f \le 1000 \text{ Hz}, \\ 1 & \text{if } d(f) \le 0.001, f \ge 2000 \text{ Hz}, \\ 10 & \text{if } d(f) \le 0.001, f \ge 2000 \text{ Hz}. \end{cases}$$

$$(6)$$

where f is the frequency of the fitness evaluation, d(f) is the absolute value of the difference between the output voltage and the target at the frequency f and W(d(f), f) is the penalty factor for the difference d(f) at the frequency f.

The set of circuits that is generated within the topology of the 3 node complete graph is examined to show how success rate is affected by different circuit representations. The best circuit is given in Fig. 3 (c). The amount of hits is equal to 86. We have found [20] that the effective design is supplied by a big ratio between the population size and the genotype length. It should be noted that it is impossible to use a theoretical framework to determine an effective circuit representation. In order to make a fair comparison, we have to compare actual simulation results.

# **5** Experimental Results

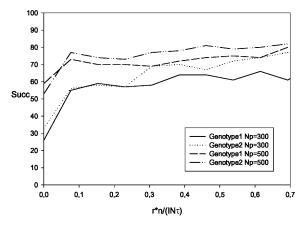

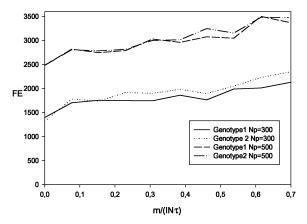

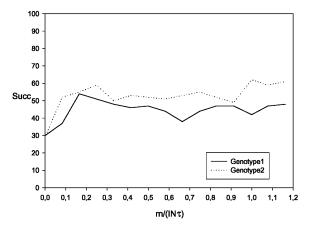

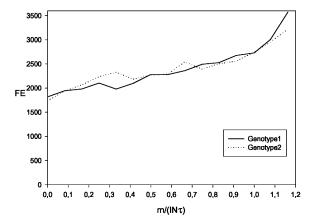

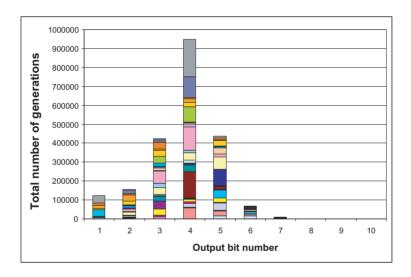

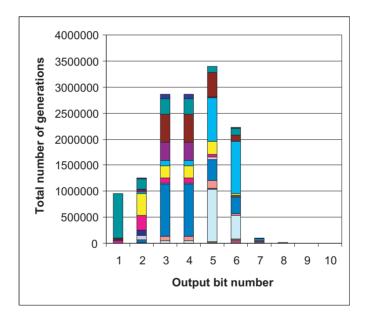

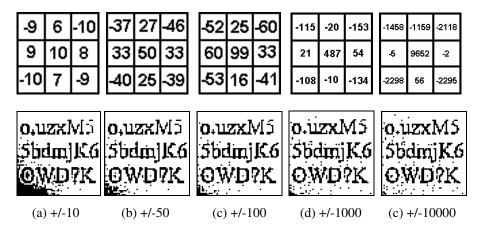

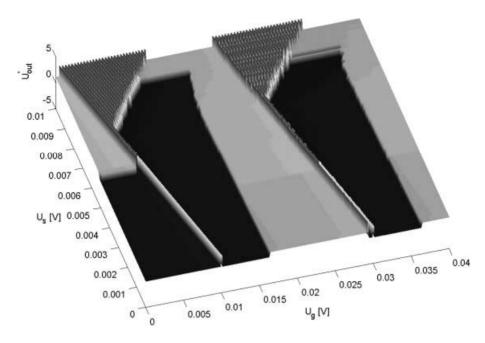

We examined the behaviour of different circuit representations for the fixed number of bits n=23 with a truncation threshold  $\tau$  from 0.02 to 0.04. Population size changes from N=300 to N=500. We consider the successful runs after 10% of the population consisted of the best solution only. Figures 4 -7 show how the success rate and the function evaluations are changed when a circuit representation is modified. The results have been obtained under assumption that the amount of iterations is less than the genotype length.

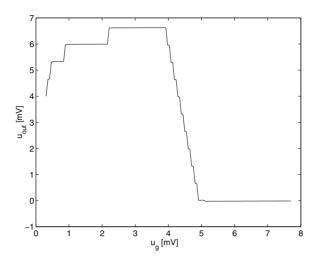

Figures 4, 5 illustrate the case in which the population size varies between N=300 and N=500 and the truncation threshold is equal to  $\tau$ =0.02. Figures 6, 7 show the case in which the population size is fixed N=300, whilst the truncation threshold is increased to  $\tau$ =0.04. The selection intensity *I* depends on a truncation threshold of  $\tau$  [17]. The most obvious fact is that the success rate is generally enhanced where the element-list circuit representation is used. The branch-list circuit description is less efficient. It is remarkable that the same number of function evaluations is required for two circuit representations approximately. Therefore, the curves have shown that the element-list circuit representation allows us to increase the success rate without the significant computational expenses.

Fig. 4. Performance comparison with varying mutation rate r for different population sizes and truncation selection with  $\tau$ =0.02. Succ is the number of times, when the best solution was found in 100 runs

Fig. 5. Performance comparison with varying mutation rate r for different population sizes and truncation selection with  $\tau$ =0.02. FE is the number of evaluation until 10% of the populations consisted of the best solution

#### 6 Discussions

Two different types of the circuit representation have been presented. The results show that the element-list circuit representation is better than the branch-list circuit representation. We are able to exploit larger population size and truncation selection with smaller  $\tau$  more effectively using the element-list circuit representation. Therefore, the assignment of topology information and parameters to the correspondent part of the genotype allow us to improve the effectiveness of evolutionary analog circuit design.

**Fig. 6.** Performance comparison with varying mutation rate r for the population size N=300 and truncation selection with  $\tau$ =0.04. Succ is the number of times, when the best solution was found in 100 runs

**Fig. 7.** Performance comparison with varying mutation rate r for the population size N=300 and truncation selection with  $\tau$ =0.04. FE is the number of evaluation until 10% of the populations consisted of the best solution

# Acknowledgments

This work was supported by INTAS (International Association for the promotion of co-operation with scientists from the New Independent States of the former Soviet Union) under grant No YSF 00 - 190. We would like to thank all members of the RWCP Group, FhG - AiS for their support, advice and criticism of this work.

Lyudmilla Zinchenko and Victor Kureichik acknowledge support by Russian Fund of Basic Research (grant 01-01-00044).

The authors also acknowledge the helpful comments of the reviewers.

#### References

- 1. Higuchi, T., Iwata, M. etc.: Real World Applications of Analog and Digital Evolvable Hardware. IEEE Transactions on Evolutionary Computation 3 (1999) 220-235

- Tyrell, A. M., Bradley, D.W.: The Architecture for a Hardware Immune System. In: Proceedings of the Third NASA/DoD Workshop on Evolvable Hardware EH 2001. Computer Press (2001) 193-200

- 3. Rutenbar, R., Liu, H., Singhee, A., Carley, L. R.: Remembrance of Circuit Past: Macromodeling by Data Mining in Large Analog Design Spaces. In: Proceedings of the ACM/IEEE Design Automation Conference (2002)

- Lohn, J. D., Colombano, S. P.: A Circuit Representation Technique for Automated Circuit Design. IEEE Transactions on Evolutionary Computation 3 (1999) 205 –219

- Yao, X., Liu, Y.: Getting Most Out of Evolutionary Algorithms. In: Proceedings of the 2002 NASA DoD Conference on Evolvable Hardware EH 2002. Computer Press (2002) 8-14

- Lohn, J., Laith, G., Colombano, S., Stassinopoulos, D.: A Comparison of Dynamic Fitness Schedules for Evolutionary Design of Amplifiers. In: Proceedings of the First NASA DoD Workshop on Evolvable Hardware EH'99. IEEE Computer Press (1999) 87-92

- Zebulum, R.S., Pacheco, R.S., Vellasco, M.A.: Analog Circuit Evolution in Extrinsic and Intrinsic Modes. In: Sipper, M., Mange, D., and Perez-Uribe, A. (eds.): Proceedings of the Second International Conference on Evolvable Systems: From Biology to Hardware (ICES98). Lecture Notes in Computer Science, Vol. 1478. Springer-Verlag, Berlin Heidelberg New York (1998) 154-165

- 8. Koza, J.R., Bennett, F. H., Andre, D., Keane, M. A.: Genetic Programming III: Darwinian Invention and Problem Solving. Morgan Kaufmann, San Francisco (1999)

- 9. Thomson, A., Layzell, P., Zebulum, R.: Explorations in Design Space: Unconventional Electronics Design Through Artificial Evolution. IEEE Transactions on Evolutionary Computation 3 (1999) 167-196

- Hartmann, M., Haddow, P., and Eskelund, F.: Evolving Robust Digital Designs. In: Proceedings of the 2002 NASA DoD Conference on Evolvable Hardware EH 2002. Computer Press (2002) 36-45

- Ando, S., Iba, H.: Analog Circuit Design with a Variable Length Chromosome. In: Proceedings IEEE Int. Congress on Evolutionary Computation. IEEE Press (2000) 994 1001

- Goh, C., Li, Y.: GA Automated Design and Synthesis of Analog Circuits with Practical Constraints. In: Proceedings IEEE Congress on Evolutionary Computation. IEEE Press (2001) 170 -177

- Goh, C., Chan, L., and Li, Y.: Performance Metrics Assessment for Pareto Fronts with Application to Analog Circuit Evolution. In: Giannakoglou, K.G., Tsahalos, D.T., Periaux, J., Papailiou, K.D., Fogarty, T. (eds.): Evolutionary Methods for Design, Optimization and Control. Theory and Engineering Applications of Computational Methods. CIMNE, Barcelona (2002) 208-213

- Grimbleby, J.B.: Hybrid Genetic Algorithms for Analogue Network Synthesis. In: Proceedings IEEE Congress on Evolutionary Computation. IEEE Press (1999) 1781 -1787

- 15. Tamplin, M.R., Hamilton, A.: Ant Circuit World: An Ant Algorithm MATHLAB Toolbox for the Design, Visualization and Analysis of Analogue Circuits. In: Proceedings of the International Conference on Evolvable Systems: From Biology to Hardware. Lecture Notes in Computer Science. Springer-Verlag, Berlin Heidelberg New York (2001)

- Mühlenbein, H., Paaß, G.: From Recombination of Genes to the Estimation of Distributions. Parallel Problem Solving from Nature PPSN IV. Lecture Notes in Computer Science, Vol. 1141. Springer-Verlag, Berlin Heidelberg New York (1996) 178-187

- Mühlenbein, H.: The Equation for Response to Selection and its Use for Prediction. Evolutionary Computation 5 (1998) 303-346

- 18. Mühlenbein, H., Mahnig, T.: Optimal Mutation Rate Using Bayesian Priors for Estimation of Distribution Algorithms, to appear.

- Mühlenbein, H., Kureichik, V.M., Mahnig, T., Zinchenko, L.A.: Evolutionary Algorithms with Hierarchy and Dynamic Coding in Computer Aided Design. In: Giannakoglou, K.G., Tsahalos, D.T., Periaux, J., Papailiou, K.D., Fogarty, T. (eds.): Evolutionary Methods for Design, Optimization and Control. Theory and Engineering Applications of Computational Methods. CIMNE, Barcelona (2002) 202-207

- Mühlenbein, H., Kureichik, V.M., Mahnig, T., Zinchenko, L.A.: Application of the Univariate Marginal Distribution Algorithm to Analog Circuit Design. In: Proceedings of the 2002 NASA DoD Conference on Evolvable Hardware EH 2002. Computer Press (2002) 93-101

- Mühlenbein, H., Kureichik, V.M., Mahnig, T., Zinchenko, L.A.: Effective Mutation Rate of Probabilistic Models for Evolutionary Analog Circuit Design. In: Proceedings of the IEEE ICAIS 2002. Computer Press (2002) 401-406

- 22. Biggs, N.: Algebraic Graph Theory. Cambridge (1974)

# Fault Tolerance via Endocrinologic Based Communication for Multiprocessor Systems

Andrew J. Greensted and Andy M. Tyrrell

Department of Electronics, Bio-Inspired Research Group, University Of York, UK YO10 5DD

{ajg112,amt}@ohm.york.ac.uk http://www.bioinspired.com

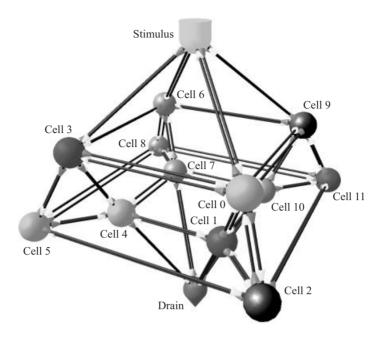

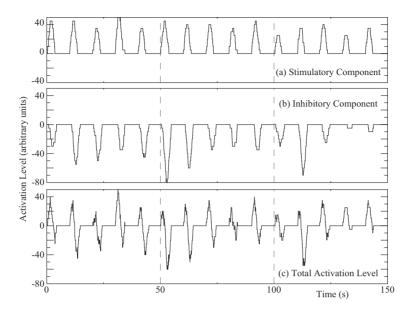

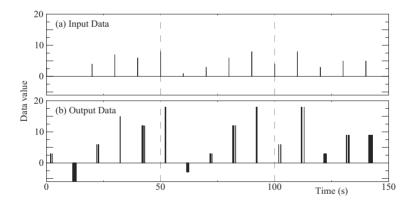

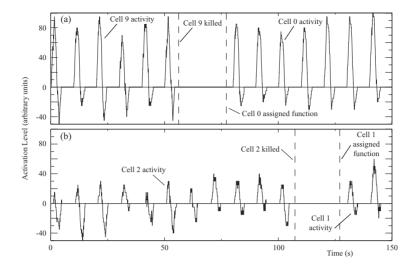

**Abstract.** The communication mechanism used by the biological cells of higher animals is an integral part of an organisms ability to tolerate cell deficiency or loss. The massive redundancy found at the cellular level is fully taken advantage of by the biological endocrinologic processes. Endocrinology, the study of intercellular communication, involves the mediation of chemical messengers called hormones to stimulate or inhibit intracellular processes.

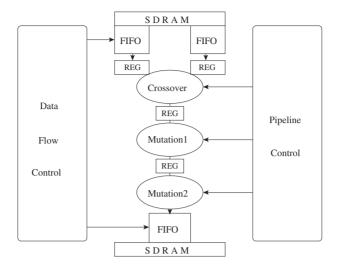

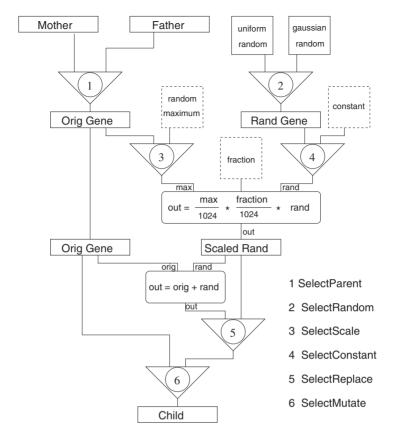

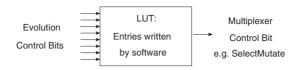

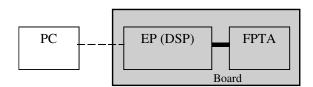

This paper presents a software model of a multiprocessor system design that uses an interprocessor communication system similar to the endocrine system. The feedback mechanisms that govern the concentration of hormones are mimicked to control data and control packets between processors. The system is able to perform arbitrary dataflow processing. Each processing stage within the system is undertaken by a separate group of microprocessors. The flow of data, and the activation of the next stage within the process is undertaken using the bio-inspired communication technique. The desired result is a system capable of maintained operation despite processor loss. The feasibility of the multiprocessor system is demonstrated by using the model to perform a simple mathematical calculation on a stream of input data.

### 1 Introduction

Biology provides a diverse source of inspiration that reaches across many fields from both artistic and scientific disciplines. Electronic Engineering is no exception.

One of the strongest impetuses for Bio-Inspired Engineering is the assistance it lends to the development of engineering design, especially where solutions via traditional techniques fall short. Such biological based solutions have led to the creation of artificial learning and pattern matching systems based on neural networks [1,2], as well as self re-configuring systems [3] based on biology's ability to evolve and adapt.

Of more interest to the area of Reliability Engineering is biology's ability to maintain operation in the face of adverse conditions. Biology is able to employ

automated fault tolerance, detection and recovery characteristics that enable organisms to remain functional despite injury. It is the desire for electronics to also exhibit these three characteristics that has led to an interest in Bio-Inspired Reliability Engineering.

Both Embryonics [4] and Artificial Immune Systems [5,6] mimic aspects of biological reliability systems. The Embryonic Architecture is capable of removing faulty circuit areas. Reconfiguration via the shifting of functionality to healthy circuitry in redundant areas returns the system to full functionality. Whereas Artificial Immune Systems provide a fault detection and removal mechanism based on the biological self, non-self principle [7].

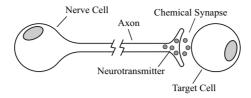

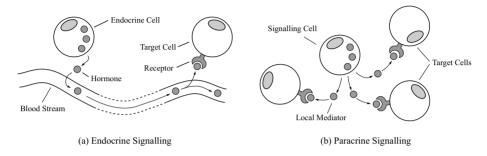

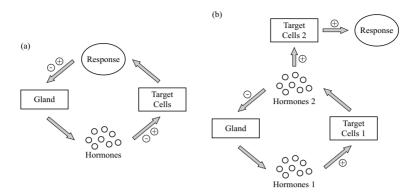

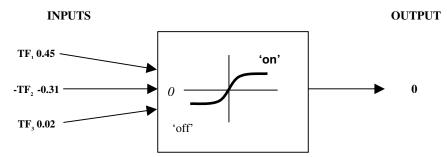

The ability of biological systems to tolerate and recover from a subsystems death is reliant upon the use of redundancy. This is a common feature present on a number of levels within biology's structural hierarchy. Society maintains activity through redundancy in individual organisms, similarly organisms can function without certain organs. However, it is the cellular level that utilizes redundancy to the greatest effect.